基于3.3-V EEPROM的高性能可编程逻辑

基于第二代多阵列矩阵的设备(PLD)(最大®)体系结构(见表1)

■ 3.3-V系统内可编程性(ISP),通过内置IEEE标准1149.1联合测试行动小组(JTAG)与先进的引脚锁定能力

–MAX 7000AE设备在系统可编程性(ISP)电路中符合IEEE标准1532

–EPM7128A和EPM7256A设备ISP电路兼容IEEE标准1532

■ 内置边界扫描测试(BST)电路符合

IEEE标准1149.1

■ 支持JEDEC Jam标准测试和编程语言(STAPL)JESD-71

■ 增强的ISP功能

–增强的ISP算法可加快编程速度(不包括EPM7128A和EPM7256A设备)–ISP_Done位以确保完成编程(不包括EPM7128A和EPM7256A设备)

–在系统内编程期间,拔出I/O引脚上的电阻器

■ 引脚与流行的5.0-V MAX 7000S设备兼容

■ 高密度PLD,可用门从600到10000

■ 扩展温度范围4.5-ns引脚对引脚逻辑延迟,计数器频率高达227.3兆赫

■ MultiVoltTM I/O接口使设备核心能够在3.3伏电压下运行,而I/O引脚与5.0-V、3.3-V和2.5-V逻辑电平兼容

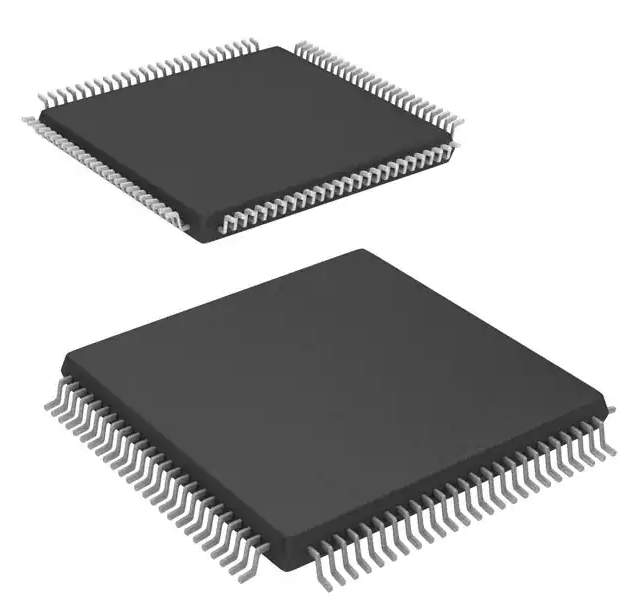

■ 各种薄型四片式扁平封装中的针数从44到256(TQFP)、塑料四边形扁平封装(PQFP-节省FineLine BGATM和塑料J引线芯片载体(PLCC)包装

■ 支持MAX 7000AE设备中的热插拔

■ 可编程互连阵列(PIA)连续布线结构实现快速、可预知的性能

■ PCI兼容

■ 总线友好架构,包括可编程转换速率控制

■ 开漏输出选项

■ 带有单个清除、预设、时钟和时钟启用控件

■ 中宏单元寄存器的可编程加电状态MAX 7000AE设备

■ 50%或更大功率的可编程节能模式每个宏细胞减少

■ 可配置扩展器产品术语分布,最多允许每个宏单元32个产品术语

■ 用于保护专有设计的可编程安全位

■ 6至10针或逻辑驱动输出启用信号

■ 两个带可选倒置的全球时钟信号

■ 增强了互连资源,提高了可路由性

■ 从I/O引脚到宏单元寄存器

■ 可编程输出转换率控制

■ 可编程接地引脚提供软件设计支持和自动地点和路线Altera针对基于Windows的PC和Sun的开发系统SPARC工作站和HP 9000系列700/800工作站

■ EDIF提供的附加设计输入和模拟支持2 0 0和3 0 0网络列表文件、参数化模块库(LPM)、,Verilog HDL、VHDL和其他与流行EDA工具的接口Cadence、Exemplar Logic、Mentor Graphics等制造商,OrCAD、Synopsys、Synplicity和VeriBest

■ Altera主编程单元的编程支持(MPU)、MasterBlaster TM串行/通用串行总线(USB)通信电缆,ByteBlasterMVTM并行端口下载电缆和BitBlaster TM串行下载电缆,以及第三方制造商的编程硬件和任何JamTM STAPL文件(.jam)、jam字节码文件(.jbc)或串行矢量格式文件-(.svf)支持在线测试仪

MAX 7000A(包括MAX 70000AE)设备是高密度、高-基于Altera第二代MAX的性能设备建筑学EEPROM采用先进的CMOS技术制造-基于MAX 7000A的设备工作电压为3.3V提供600到10000个可用门、ISP、引脚到引脚延迟,速度高达4.5 ns,计数器速度高达227.3 MHz。-4、-5、-6、-7和一些-10速度等级与定时兼容PCI Special Interest Group(PCI)33 MHz操作要求SIG)PCI本地总线规范,2.2版。见表2。MAX 7000A架构支持100%晶体管到晶体管逻辑SSI、MSI和LSI逻辑的(TTL)仿真和高密度集成功能。它可以轻松集成多个设备,包括PAL、GAL和22V10设备。MAX 7000A设备有多种包,包括PLCC、BGA、FineLine BGA、Ultra FineLineBGA、PQFP和TQFP包。

在线客服

在线客服